界限扫描仪检测(Boundary scan)是为了更好地处理pcb电路板(PCB)上集成ic与集成ic中间的互联检测而提起的一种解决方法。它与內部扫描仪有显著的差别,前面一种是在电源电路的键入/导出端口号提升扫描仪模块,并将这种扫描仪模块连接成扫描仪通道,后者是将电源电路中一般的时钟频率模块更换变成具备扫描仪工作能力的时钟频率模块,再将他们连接成扫描仪通道。

一、界限扫描仪检测基本原理

最先是射频收发器检测,即可以对集成ic自身开展检测和调节,使集成ic工作中在一切正常作用方式,根据键入端键入检测矢量素材,并仔细观察串行通信挪动的输入回应开展调节。

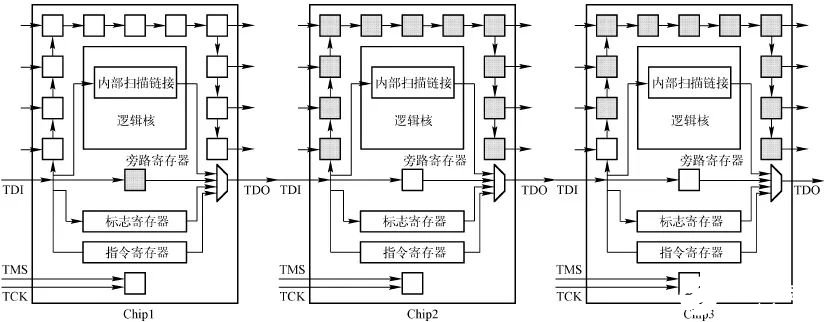

次之是板级检测,检验电子器件和PCB中间的互联。完成基本原理是将一块PCB上全部具备界限扫描仪的IC中的扫描仪存储器联接在一起,根据一定的检测矢量素材,可以发觉元器件是不是遗失或是放置不正确,与此同时可以检验管脚的引路和短路故障问题。

最终是系统软件级检测,在板级集成化后,可以根据对板上CPLD或是Flash的可视化编程,完成系统级检测。

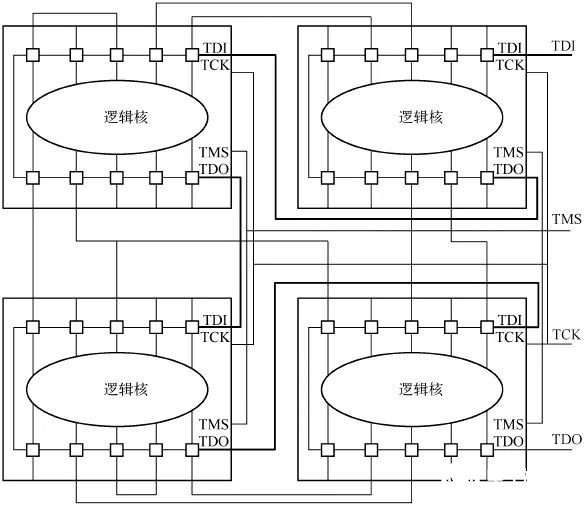

在其中,最首要的功用是开展板级集成ic的互联检测,如下图1所显示。

图1 根据界限扫描仪的板级互联检测

二、IEEE 1149.1规范

界限扫描仪是欧美国家一些大企业协同创立的一个机构——协同检测行为工作组(JTAG),为了更好地处理pcb电路板(PCB)上集成ic与集成ic中间互联检测而提起的一种解决方法。因为该计划方案的合理化,它于1990年被IEEE采取而变成一个规范,即IEEE 1149.1。该标准了界限扫描仪的测试端口、检测构造和实际操作命令。

1.IEEE 1149.1构造

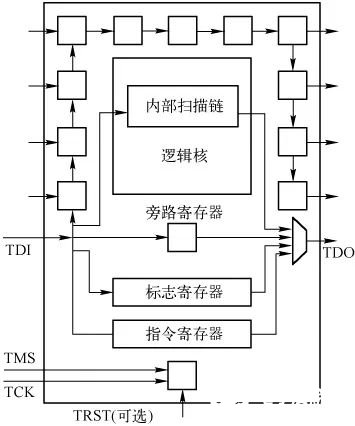

IEEE 1149.1构造如下图2所显示,其包括TAP控制板和存储器组。在其中,TAP控制板如下图3所显示;存储器组包含界限扫描仪存储器、旁通存储器、标志寄存器和指令寄存器,关键端口号为TCK、TMS、TDI、TDO,此外还有一个客户可选用的端口号TRST。

图2 IEEE 1149.1构造

图3 TAP控制板

2.端口号界定如下所示

(1)TCK(Test Clock)

界限扫描仪设计方案中的检测钟表是单独的,因而与原先IC或PCB上的钟表是不相干的,还可以重复使用原先的钟表。

(2)TMS(Test Mode Select)

因为在检测流程中,必须有数据信息捕获、挪动、中止等差异的工作模式,因而必须有一个数据信号来操纵。在IEEE 1149.1中,仅有那样一根操纵数据信号,根据相应的键入编码序列来明确工作模式,选用有限状态机来完成。该数据信号在检测钟表TCK的上升沿取样。

(3)TDI(Test Data In)

以串行通信方法键入的数据信息TDI有二种。一种是命令数据信号,送进指令寄存器;另一种是数据测试(鼓励、导出回应和别的数据信号),它键入到对应的界限扫描仪存储器中去。

(4)TDO(Test Data Out)

以串行通信导出的数据信息也是有二种,一种是以指令寄存器挪动出去的命令,另一种是以界限扫描仪存储器挪动出去的数据信息。

此外,还有一个可选端口号TRST,为检测系统软件校准数据信号,功效是强制性校准。

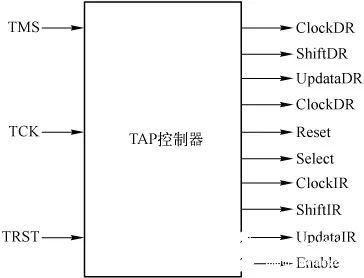

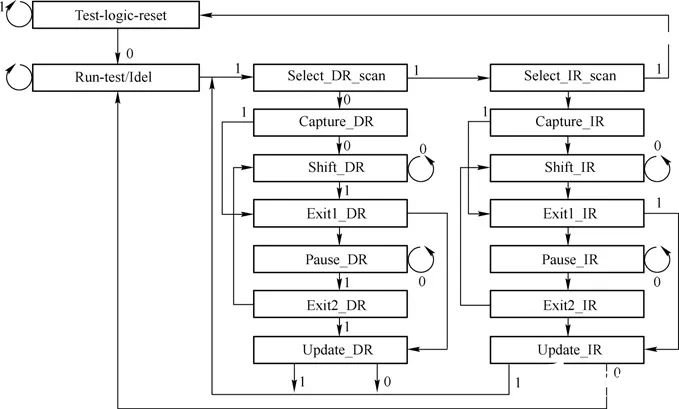

3.TAP控制板

TAP控制板的功效是将串行通信键入的TMS数据信号开展译码器,使界限扫描仪系统软件进到对应的测试模式,而且造成该方式下所需的每个操纵数据信号。IEEE 1149.1的TAP控制板由有限状态机来完成,图4所显示为情况迁移图。DR表明数据寄存器,IR表明指令寄存器。

图4 TAP控制板的情况迁移图

4.存储器组

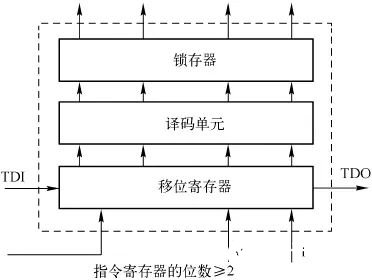

(1)指令寄存器(IR,Instruction Register)

如下图5所显示,指令寄存器由移位寄存器和锁存构成,长短相当于命令的长短。IR可以联接在TDI和TDO的两边,经TDI串行通信键入命令,而且送进锁存,储存当今命令。在这里两部份中有一个译码器模块,承担鉴别当今命令。因为JTAG有3个强制性命令,因此该存储器的间距最少为2位。

图5 指令寄存器

(2)旁通存储器(BR,Bypass Register)

旁通存储器还可以立即联接在TDI和TDO两边,仅有1位构成。若一块PCB上面有好几个具备界限扫描仪设计方案的IC,可将每一个IC中的界限扫描仪链串连起來。假如这时必须对这其中的某好多个IC开展检测,就可以根据BYPASS命令来旁通不必检测的IC。如下图6所显示,假如想要检测Chip2和Chip3,则在TDI键入110000就可以配备旁通存储器,这时Chip1的旁通存储器被置位,表明该集成ic在检测流程中被旁通。

图6 旁通存储器应用例举

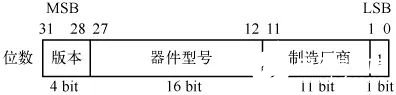

(3)标志寄存器(IDR,Identification Register)

如下图7所显示,在一般的界限扫描仪设计方案中,都包括一个干固有该元器件标示的存储器,它是一个32位的规范存储器,其內容有关于该元器件的版本信息、元器件型号规格、生产商等信息内容,主要用途是在PCB生产制造网上,可以查验IC的规格和版本号,便于维修和更换。

在元器件标志寄存器的规范文件格式中,最少位(第0位)为1,用以鉴别标志寄存器和旁通存储器的标志位。第1~11位为生产商的标志位。依据国际性协同电子器件元器件工程项目联合会所确立的计划方案,这11位共容许有2032个生产商的标志。第12~27位表明元器件的型号规格,累计可以表明216=65536种不一样的型号规格。剩下的4位表明同一型号规格元器件的不一样版本号。

图7 标志寄存器

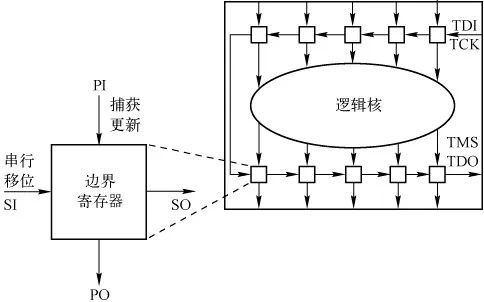

(4)界限扫描仪存储器

界限扫描仪存储器是界限扫描仪中最重要的结构单元,它进行数据测试的键入、导出锁存和挪动全过程中必需的数据信息实际操作。其工作中在多种多样方式,最先是达到扫描仪链上的串行通信挪动方式,次之是一切正常方式下电源电路的数据信息捕获和升级,如下图8所显示。

图8 界限扫描仪存储器

运用界限扫描仪存储器可给予如下所示的关键检测作用:

▪ 对被测IC的外界电源电路进行检测,如能测IC中间的互联,这时可以采用外界检测命令EXTEST;

▪ 应用INTEST开展被测电源电路的內部自测试;

▪ 对键入、导出数据信号开展取样和升级,这时可以彻底不危害关键时序逻辑电路的运行状态。

5.有关命令

JTAG要求了3个强制性命令:EXTEST、BYPASS、SAMPLE/PRELOAD。

(1)EXTEST:外检测命令

外检测命令适用于检测IC和PCB中间的连线或界限扫描仪设计方案之外的时序逻辑电路。实行该命令的关键实际操作为,将检测矢量素材串行通信挪动至界限扫描仪存储器,以鼓励待测的连线或外界时序逻辑电路,与此同时该存储器又捕获回应数据信息,并串行通信移出来检测結果,便于查验。

(2)BYPASS:旁通命令

这也是一条由1构成的全1命令串,它的功用是挑选该IC中的旁通存储器BR,决策该IC是不是被检测。

(3)SAMPLE/PRELOAD:取样/内置命令

取样命令用以不危害关键逻辑性一切正常作业的前提下,将界限扫描仪设计方案中的并行处理键入的数据信号捕获至界限扫描仪存储器中,在测验时,根据取样命令捕获所检测时序逻辑电路的回应。内置命令作用与取样基本一致,仅仅这时装进界限扫描仪存储器的数据信息是程序编写者已经知道或明确的。除开以上务必的命令外,JTAG还界定了一部分可选用的命令:INTEST、IDCODE、RUNBIST、CLAMP、HIGHZ。

▪ INTEST为内检测命令,用以检测关键时序逻辑电路。实行全过程与外检测命令基本上类似,仅仅因为被测另一半的部位恰好相反,它的奖励端和回应检测端正好反过来。

▪ IDCODE命令用以从标志寄存器中取下标示编码。

▪ RUNBIST为运作自测试命令,用于实行被测逻辑性的自测试作用,必须确保电源电路本身就具备

▪ 自测试构造。

▪ CLAMP是部件命令,有两个作用,一是使旁通存储器为0,另一个是使界限扫描仪存储器BSR的输入输出为一组给出的固定不动脉冲信号。

▪ HIGHZ是攻击高阻命令,可以使IC的全部导出端都呈高阻情况,即失效情况。

三、界限扫描仪检测对策和相关的专用工具

1.板级检测对策

运用界限扫描仪IEEE 1149.1开展板级检测的对策分下列3步。

① 依据IEEE 1149.1规范创建界限扫描仪的检测构造。

② 运用界限扫描仪检测构造,对被测一部分中间的联接开展矢量素材键入和响应分析。这也是板级检测的关键阶段,也是界限扫描仪构造的关键运用。可以用于检验因为电气设备、机械设备和溫度造成的板级集成化常见故障。

③ 对单独一个关键逻辑性开展检测,可以复位该逻辑性而且运用其自身的检测构造。

2.有关EDA专用工具

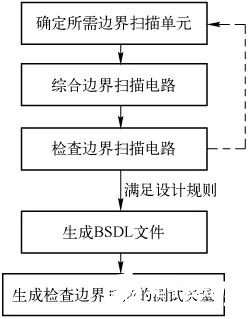

工业领域关键选用的界限扫描工具为Mentor的BSDArchitect和Synopsys的BSD Compiler。之后者为例子,其关键设计流程如下图9所显示。该步骤会转化成BSDL文档,该文件是界限扫描仪检测软件更新,该文件內容包含管脚界定和界限扫描仪链的构成构造。一般的ATE可以鉴别该文件,并自动生成相对应的测试代码,进行集成ic在板上的泄露电流等主要参数的检测。

图9 界限扫描仪设计流程

责编:gt

该文章内容提高散播新技术应用新闻资讯,很有可能有转截/引入之状况,若有侵权行为请联络删掉。

上一篇: 什么是免洗无锡膏?有哪些特征?

下一篇: 加速度传感器的差容式力平衡原理技术简述

派旗纳米·官方网站

派旗纳米·官方网站