电磁兼容测试性就是指电子器件机器设备在一些磁感应自然环境中仍可以融洽、合理地开展工作中的工作能力。电磁兼容测试性设计方案的效果是使电子产品既能抑止各种各样外界的影响,使电子在相应的磁感应自然环境中可以正常的工作中,与此同时又能降低电子产品自身对其他电子产品的干扰信号。

1、挑选有效的输电线总宽

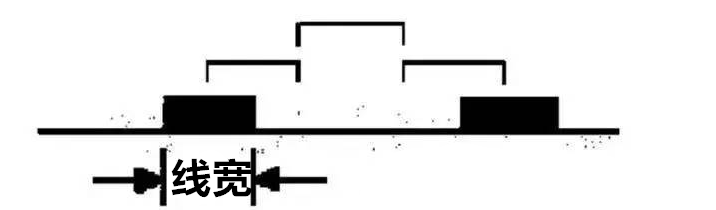

因为磁法勘探电流量在印刷线框上所发生的冲击性影响主要是由印刷输电线的电感器成份导致的,因而应尽可能减少印刷输电线的电感器量。印刷输电线的电感器量与其说长短正相关,与其说总宽反比,因此短而精的输电线对抑止影响是有益的。钟表导线、行控制器或系统总线控制器的电源线经常乘载大的磁法勘探电流量,印刷输电线要尽量地短。针对分立元件电源电路,印制导技术线距度在1.5mm上下时,就可以彻底符合要求;针对电子器件,印刷输电线总宽可在0.2~1.0mm中间挑选。间隔最好线距的二倍,核心距3倍

2、选用合理的走线对策

选用公平布线可以减小输电线电感器,但输电线间的互感器和遍布电容器提升,假如合理布局容许,最好是选用井字型网状走线构造,具体方法是印制电路板的一面横着走线,另一面竖向走线,随后在交叉式孔处用镀覆孔相接。

3、合理地抑止串扰

为了更好地抑止印制电路板输电线间的串扰,在设计方案走线时尽量减少远距离的公平布线,尽量拉下线与线中间的间距,电源线与接地线及电源插头尽量不交叉式。在一些对影响十分比较敏感的电源线中间设定一根接地装置的印刷线,可以合理地抑止串扰。

4、为了防止高频率数据信号根据印刷输电线时发生的电磁波辐射,在pcb电路板走线时,还应留意以下几个方面:

(1)尽量避免印刷输电线的不连续性,比如输电线总宽不必基因突变,输电线的转角应超过90度严禁环形布线等。

(2)时钟信号导线最非常容易造成电磁波辐射影响,布线时要与接地线控制回路相挨近,控制器应紧挨着射频连接器。

(3)系统总线控制器应紧靠其欲推动的系统总线。针对这些离去pcb电路板的导线,控制器应牢牢地挨着射频连接器。

(4)系统总线的走线应每二根电源线中间夹一根数据信号接地线。最好牢牢地挨着最不重要的详细地址导线置放地控制回路,由于后者常乘载高频率电流量。

5、抑止反射面影响

为了更好地抑止发生在印刷线框终端设备的反射面影响,除开独特必须以外,应尽量减少印刷线的尺寸和选用慢速度电源电路。必需时可放终端设备配对,即在同轴电缆的尾端对地和开关电源端各加接一个同样电阻值的配对电阻器。依据工作经验,对一般速率迅速的TTL电路,其印刷线框长而10cm以上时就应选用终端设备配对对策。匹配电阻的电阻值应依据集成电路芯片的导出驱动电流及消化吸收电流量的最高值来决策。

6、电源设计全过程中选用音频信号线走线对策

走线十分挨近的音频信号对彼此之间也会相互之间密切藕合,这类相互之间中间的藕合会减小EMI发送,通常(自然还有一些除外)音频信号也是快速数据信号,因此极速设计方案标准通常也都适用音频信号的走线,尤其是设计方案同轴电缆的电源线时更是如此。这就代表大家务必十分慎重地设计方案电源线的走线,以保证电源线的特点特性阻抗沿电源线各个地方持续而且维持一个参量。

在差分信号线对的合理布局走线全过程中,大家需要差分信号线对中的2个PCB线完全一致。这就代表着,在具体运用中应当尽最高的勤奋来保证差分信号线对中的PCB线具备彻底一样的特性阻抗而且走线的尺寸也完全一致。差分信号PCB线通常一直成对走线,并且他们中间的间距沿途对的方位在任何部位都维持为一个参量不会改变。一般而言,差分信号线对的合理布局走线一直尽量地挨近。

该文章内容提高散播新技术应用新闻资讯,很有可能有转截/引入之状况,若有侵权行为请联络删掉。

派旗纳米·官方网站

派旗纳米·官方网站