IMEC明确提出了一种扇型圆晶级封装形式的新方式,可达到更密度高的,更带宽测试的集成ic到集成ic联接的要求。 IMEC的高級技术工程师Arnita Podpod和IMEC Fellow及3D信息系统集成方案的项目负责人Eric Beyne详细介绍了该技术性,探讨了具体的试炼和使用价值,并列结构出了潜在性的运用。

圆晶级封装形式: 适用移动智能终端的有诱惑力的封装形式解决方法

现如今,很多电子器件系统软件依然由好几个元器件构成,这种元器件在集成ic激光切割后独立封装形式,而且应用传统式的印刷线路板互联。 殊不知,这些年,针对更“严苛”的运用就必须优秀的3D集成化和互联技术性。 由于这大大的减少了电子控制系统的规格,而且完成了子电源电路中间更快,更短的联接。 这种技术性之一是圆晶级封装形式(Wafer Level Packaging),即好几个裸片在圆晶上与此同时被封装形式。 因为全部圆晶现在是一次性封装形式,因而该解决方法比传统式封装形式计划方案成本费更低。 除此之外,所得的封装形式后芯片尺寸更小,更薄,这也是智能机等规格比较敏感机器设备十分重视的。 在现如今的智能机上,大约5/7的处理器是圆晶级封装形式的,并且数目仍在持续提升。

扇入和扇出

有二种关键类别的圆晶级封装形式: 扇入式和扇出式,他们的差异关键在重遍布层中。 重遍布层(通常是有机化学层)用以将裸片的插口(I/ O)再次走线到需要的(凸块)部位。 扇入便是重遍布层迹线向内走线,产生一个十分小的封装形式(大概相匹配于裸片自身的规格)。 可是,重遍布加工工艺还能够用以拓展封装形式的可以用地区,拓宽集成ic接触点到超过芯片尺寸就建立了扇出式封装形式。 通常,这类扇出WLP(FO-WLP)技术性给予比扇入式WLP技术性大量的I /O总数。

在移动智能终端中,扇出圆晶级封装形式已经逐渐替代更传统式的封装形式上封装形式(PoP)储存器逻辑性集成ic层叠解决方法。

这种PoP比扇出式厚得多,而且遭受的互联网络带宽和相对密度及其比较有限的间隔调整图片大小(几百微米)的限定。 在这种使用中,FO-WLP也强于别的可以用的带宽测试3D技术性,比如3D层叠(在其中逻辑性管芯中的网络热点很有可能危害储存器数据信息维持工作能力)或2.5D层叠(在其中较长的互联线造成较高的互联输出功率和附加成本费)。

2个基本上的“扇出”步骤

过去两年中,早已不断涌现了各种各样FO-WLP方式,以达到对高数据速率和宽I/ O总数的日益提高的要求,并达到对封装形式上提升的作用集成化的要求。 全部这种方式都从2个基本上的扇出步骤中的一个逐渐: “mold first”或“redistribution layer first”。

在“mold first “加工工艺中,最先将裸片拼装在临时性媒介上,随后开展集成ic覆盖成形。 环氧树脂胶的功用是维护每个部件并将他们粘在一起。 在最终,制做重各分部层并创建联接。 在“redistribution layer first”加工工艺中,在重遍布层的加工工艺以后再做裸片拼装和集成ic注塑工艺。

这种方式中的每一种都是有其自己的一些缺陷。 比如,在“mold first “加工工艺中,裸片通常在注塑工艺以后产生挪动,这促使完成小于100μm的互联节径十分具备趣味性。 “redistribution layer first”加工工艺中,可完成的相对密度遭受(有机化学)再遍布层可以完成的线和空间分辨率的限定。

Flip-chip on FO-WLP: 一种新的“扇出”方式,可完成更多的互联相对密度

为了更好地达到更密度高的,更带宽测试的集成ic到集成ic联接的要求,IMEC精英团队在300mm圆晶上研发了一种新奇的FO-WLP方式,称之为Flip-chip on FO-WLP。

这一加工工艺归属于“mold first ”加工工艺,但与标的“mold first ”加工工艺反过来,集成ic在覆盖成形以前早已相互之间联接。

下边将表述这类办法的优势及其试炼。

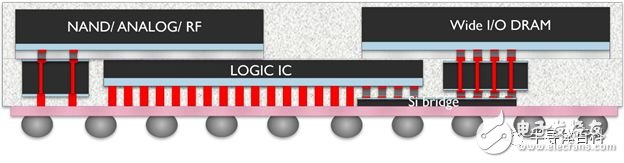

核心部件: through package vias(TPV)和硅桥

这类新的扇出方法的早已在TQV上获得认证。 TQV由七个单独的主板芯片组件构成: Wide I / O DRAM,闪存芯片,逻辑性,2个TPV裸片和2个硅桥。 由于这一TQV仅仅用以认证。 因而,逻辑性和微处理器集成ic并不是多功能的: 他们是“仿真模拟”裸片,用以检测突点联接中间的电持续性。

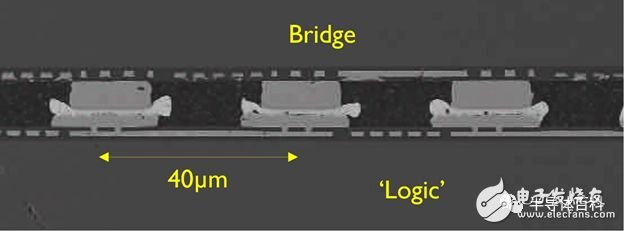

硅桥和TPV裸片是完成密度高的联接的核心部件。 TPV裸片具备硅埋孔(TSV)和40μm节径的突点。 硅桥具备40μm和20μm节径的凸块。 这种元器件在作用集成ic(比如逻辑性和微处理器集成ic)中间产生中继,完成具备20μm凸块节径的极高集成ic到集成ic互联相对密度。

与规范“mold first “加工工艺对比,另一个重要加工工艺是裸片间的密切指向。 在该重要拼装流程中,必须将每个裸片高精密地置放并临时性键合在平缓的硅晶圆上。

Flip-chip on FO-WLP芯片概念图

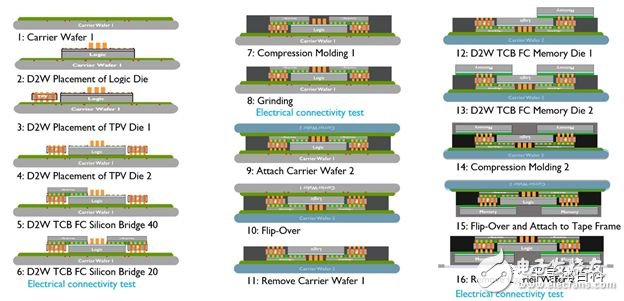

生产流程关键点

在拼装生产流程的第一流程中,将TPV片和逻辑性裸片置放在覆有临时性键合层的媒介集成ic上。 下面,应用压合紧密连接(TCB)加工工艺联接硅桥(具备40μm和20μm的凸块间隔)与逻辑性裸片和TPV裸片。 在该加工工艺流程中,具备40μm节径的凸块联接到逻辑性裸片的左边和TPV裸片。 20μm间隔凸块联接到逻辑性裸片的右边。 在下一流程中,集成ic由液体化学物质注塑工艺。 检测表明彻底添充,乃至是硅桥底下方地区。 随后,根据研磨抛光曝露铜柱,便于稍候与重遍布层联接。 在将减薄的集成ic旋转并第二媒介引线键合,并清除第一媒介。 以后,应用倒装句高端芯片拼装储存器裸片。 最终,再一次圆晶级注模和第二媒介的清除进行生产流程。 在生产流程中间,会开展持续性检测以认证电源电路详细。 最终获得封装形式薄厚仅为300-400μm的集成ic(不包括焊球)。

Flip-chip on FO-WLP集成ic: 封装形式生产流程

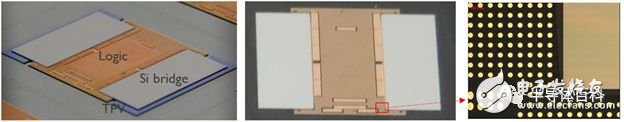

图例了裸片置放和中继以后的流程5至8(左); (中)在注塑加工和反面碾磨以后和(右)曝露的Cu柱在封装形式表皮表面

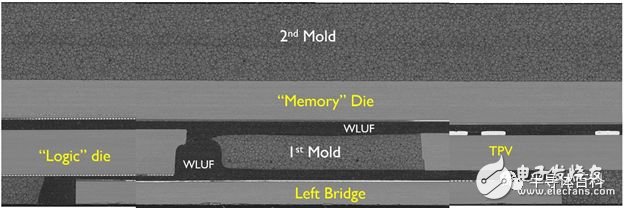

最后的第二圆晶级成形以后的截面

关键试炼和解决方法

这套生产流程产生了一系列试炼,必须摆脱这种试炼才可以保证具备极高集成ic到集成ic互联相对密度的多功能封装形式解决方法。

在其中一个问题是在拼装生产流程中裸片很有可能偏斜,尤其是针对长而窄的TPV裸片和硅桥。 这种裸片的偏斜很有可能会毁坏部件中间的互联。 为了更好地评定偏斜是不是及其什么时候产生,IMEC精英团队选用不一样的能量来置放TPV裸片。 该精英团队观查到,即使是更大的贴装力,偏斜也限定在5μm下列,这充足低以维持连通性。

下面是,逻辑性裸片和TPV裸片中间的指向,这早已导致了十分大的关心,而且被觉得是FO-WLP加工工艺的主要因素。

逻辑性裸片和TPV裸片彼此之间靠的十分近,而且必须精准的指向流程以完成后面的硅桥40μm和20μm凸块节径层叠。 比如,为了更好地完成需要的20μm凸块间隔,仅可以忍受逻辑性裸片和TPV裸片中间的较大 /-3μm的指向偏差。 为了更好地完成这类很小的偏差,该精英团队将指向标识引进到媒介和裸片设计方案中。 逻辑性裸片最先与媒介指向。 下面,置放TPV裸片,与媒介指向因而与逻辑性管芯指向。 最终,应用高精密层叠压合引线键合机器设备来置放硅桥。

硅桥联接键合在逻辑性裸片上的实例

在接着的模制作而成的全过程中,裸片依然会挪动,进而毁坏TPV和硅桥中间或逻辑性裸片和硅桥中间的凸块联接。 因而,IMEC精英团队在成形以前和之后开展了专业的电气测试。 测试表明,橡塑制品全过程不容易危害联接的一致性。 根据这种結果,可以假定,假如这种裸片在注塑加工时挪动,他们应该是在同样的方位中作总体偏移,因此不容易毁坏连通性。

汇总和未来发展趋势

根据这类新奇的方式,IMEC精英团队在扇出自然环境中展现了具备20μm凸块节径的刷新纪录的集成ic到集成ic互联相对密度。 在一段时间的未来,该技术性将获得进一步改善,电气设备和微波射频个人行为将以不一样的配备开展评定。

所确立的技术性针对移动智能终端特别是在有诱惑力,因为它以十分小的样子因素完成了经济发展高效的WideI / O储存器到逻辑性集成ic互联。

最后,FO-WLP上的倒装句集成ic也有可能变成异构体集成化的适用技术性,看准性能卓越运用。 它可以给予一种在电气设备相对高度互联的封装形式中集成化好几个裸片的方式,包含大数据处理,储存器和光纤通信控制模块。

该文章内容提高散播新技术应用新闻资讯,很有可能有转截/引入之状况,若有侵权行为请联络删掉。

上一篇: 一款详细的射频PCB设计案例分析

派旗纳米·官方网站

派旗纳米·官方网站